(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2017-120972

(P2017-120972A)

(43) 公開日 平成29年7月6日(2017.7.6)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>H04N 5/341</b> (2011.01) | H04N 5/335 | 410 2H04O   |

| <b>H04N 5/351</b> (2011.01) | H04N 5/335 | 510 4C161   |

| <b>H04N 5/372</b> (2011.01) | H04N 5/335 | 720 5C024   |

| <b>H04N 5/232</b> (2006.01) | H04N 5/232 | Z 5C122     |

| <b>A61B 1/04</b> (2006.01)  | A61B 1/04  | 372         |

審査請求 未請求 請求項の数 4 O L (全 16 頁) 最終頁に続く

|           |                              |          |                                                                                               |

|-----------|------------------------------|----------|-----------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2015-256222 (P2015-256222) | (71) 出願人 | 000000376<br>オリンパス株式会社<br>東京都八王子市石川町2951番地                                                    |

| (22) 出願日  | 平成27年12月28日 (2015.12.28)     | (74) 代理人 | 100076233<br>弁理士 伊藤 進                                                                         |

|           |                              | (74) 代理人 | 100101661<br>弁理士 長谷川 靖                                                                        |

|           |                              | (74) 代理人 | 100135932<br>弁理士 篠浦 治                                                                         |

|           |                              | (72) 発明者 | 本田 誠也<br>東京都渋谷区幡ヶ谷2丁目43番2号 オ<br>リンパス株式会社内                                                     |

|           |                              |          | F ターム (参考) 2H040 GA00<br>4C161 BB02 CC06 DD03 JJ11 LL02<br>NN01 NN03 SS03 UU03 UU09<br>最終頁に続く |

## (54) 【発明の名称】撮像装置

## (57) 【要約】

【課題】内視鏡自体の遮光構造、配光特性または組立精度等によらず、固体撮像素子における有効画素開始位置を正確に算出する。

【解決手段】光電変換部において生成した信号電荷に基づいて撮像信号を生成し出力するための複数の画素を備えた撮像素子22と、撮像素子22の基板電圧V<sub>SUB</sub>を第1の電圧と当該第1の電圧より低い電圧であって前記光電変換部に電荷を逆注入可能とする第2の電圧、とに切り替えて設定することを可能とする基板電圧V<sub>SUB</sub>制御部26と、撮像信号のエッジを抽出し有効画素開始位置を算出するFPGA25と、を備え、有効画素開始位置を算出する際は、基板電圧V<sub>SUB</sub>を第2の電圧に設定して光電変換部に電荷が逆注入された状態にせしめた後、前記エッジを抽出して有効画素開始位置を算出する。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

入射光に応じて光を光電変換して信号電荷を生成する複数の光電変換部を有し、当該光電変換部において生成した信号電荷に基づいて撮像信号を生成し出力するための複数の画素を備えた固体撮像素子と、

前記固体撮像素子の基板電圧を、所定の第1の電圧と当該第1の電圧より低い電圧であつて前記光電変換部に電荷を逆注入可能とする第2の電圧、とに切り替えて設定することを可能とする基板電圧制御部と、

前記固体撮像素子から出力した前記撮像信号のエッジを抽出し、前記複数の画素に係る有効画素開始位置を算出する有効画素開始位置算出部と、

を備え、

前記有効画素開始位置算出部は、前記基板電圧を前記第2の電圧に設定するよう前記基板電圧制御部を制御して前記光電変換部に電荷が逆注入された状態にせしめた後、前記固体撮像素子から出力した前記撮像信号のエッジを抽出し、前記複数の画素に係る有効画素開始位置を算出する

ことを特徴とする撮像装置。

**【請求項 2】**

前記有効画素開始位置算出部により算出された前記有効画素開始位置に係る情報を記憶する記憶部を備える請求項1に記載の撮像装置。

**【請求項 3】**

前記有効画素開始位置に係る情報は、前記有効画素開始位置と水平同期信号との位相差に係る情報である

ことを特徴とする請求項2に記載の撮像装置。

**【請求項 4】**

前記固体撮像素子に接続され、前記撮像信号を伝送する伝送ケーブルを備え、

前記有効画素開始位置に係る情報は、前記伝送ケーブルを伝送する前記撮像信号の遅延量の情報である

ことを特徴とする請求項3に記載の撮像装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、撮像装置に関し、特に、固体撮像素子における有効画素開始位置を算出可能とする撮像装置に関する。

**【背景技術】****【0002】**

被検体の内部の被写体を撮像する内視鏡、及び、内視鏡により撮像された被写体の観察画像を生成する画像処理装置等を具備する内視鏡システムが、医療分野及び工業分野等において広く用いられている。

**【0003】**

このような内視鏡システムにおける内視鏡としては、従来、被写体像を入光する固体撮像素子として例えばCCDイメージセンサを採用し、また、この固体撮像素子から出力されるアナログ撮像信号を伝送するケーブルを内部に配設する内視鏡が知られている（特許文献1参照）。

**【0004】**

一方、この種の伝送ケーブルを配設する内視鏡においては、近年、撮像素子の高画素化および高速化に伴い、当該伝送ケーブル内を伝送する撮像信号の遅延が後段側（例えば、ビデオプロセッサ）における画像処理に影響を及ぼすようになってきた。

**【0005】**

しかしながら、この伝送ケーブルにおける撮像信号の遅延量は、主として当該伝送ケーブルのケーブル長に起因することが知られていることから、従来、内視鏡ごとに予め当該

遅延量を求めておくことにより、上述した後段側における画像処理への影響を排除することができる可能となっている。

#### 【0006】

具体的には、内視鏡における固体撮像素子に一定の光を照射し、この固体撮像素子における複数の画素のうち当該照射光に反応し始める画素を有効画素の開始位置とみなすこととで、伝送ケーブルに起因する遅延量を求め、この遅延量を当該内視鏡固有の遅延量として所定のメモリに記憶し、後段側の画素処理においてこの遅延量を考慮することにより、悪影響を排除することが可能となる。

#### 【0007】

すなわち、当該固体撮像素子における有効画素開始位置を正確に算出することができれば、この有効画素開始位置の算出結果と、上述した伝送ケーブルに由来する遅延に係るパラメータとに基づいて、当該内視鏡固有の「正しい遅延量」を求めることができることから、上述した「有効画素開始位置」を正確に算出することが重要となる。

10

#### 【先行技術文献】

#### 【特許文献】

#### 【0008】

【特許文献1】特開2009-106442号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

一方、この種の内視鏡においては、従来、内視鏡自体の遮光構造、配光特性または組立精度等により、固体撮像素子における光に反応し始める画素の位置（すなわち、上述した有効画素開始位置）を正確に求めることが困難となる虞があった。

20

#### 【0010】

この場合、すなわち、有効画素開始位置を誤って認識してしまうと、上述した理由により、伝送ケーブルに起因する「遅延量」についても間違って認識しまうこととなり、上記の「正しい遅延量」を得ることができない虞があった。

#### 【0011】

そして、この「正しい遅延量」を得ることができない場合、後段の画像処理において、例えば、色ずれ、または、レンズとの中心位置ずれという不具合を生じる虞があった。

30

#### 【0012】

本発明は上述した事情に鑑みてなされたものであり、内視鏡自体の遮光構造、配光特性または組立精度等によらず、固体撮像素子における有効画素開始位置を正確に算出することができる撮像装置を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0013】

本発明の一態様の撮像装置は、入射光に応じて光を光電変換して信号電荷を生成する複数の光電変換部を有し、当該光電変換部において生成した信号電荷に基づいて撮像信号を生成し出力するための複数の画素を備えた固体撮像素子と、前記固体撮像素子の基板電圧を、所定の第1の電圧と当該第1の電圧より低い電圧であって前記光電変換部に電荷を逆注入可能とする第2の電圧、とに切り替えて設定することを可能とする基板電圧制御部と、前記固体撮像素子から出力した前記撮像信号のエッジを抽出し、前記複数の画素に係る有効画素開始位置を算出する有効画素開始位置算出部と、を備え、前記有効画素開始位置算出部は、前記基板電圧を前記第2の電圧に設定するよう前記基板電圧制御部を制御して前記光電変換部に電荷が逆注入された状態にせしめた後、前記固体撮像素子から出力した前記撮像信号のエッジを抽出し、前記複数の画素に係る有効画素開始位置を算出する。

40

#### 【発明の効果】

#### 【0014】

本発明によれば、内視鏡自体の遮光構造、配光特性または組立精度等によらず、固体撮像素子における有効画素開始位置を正確に算出することができる撮像装置を提供すること

50

ができる。

**【図面の簡単な説明】**

**【0015】**

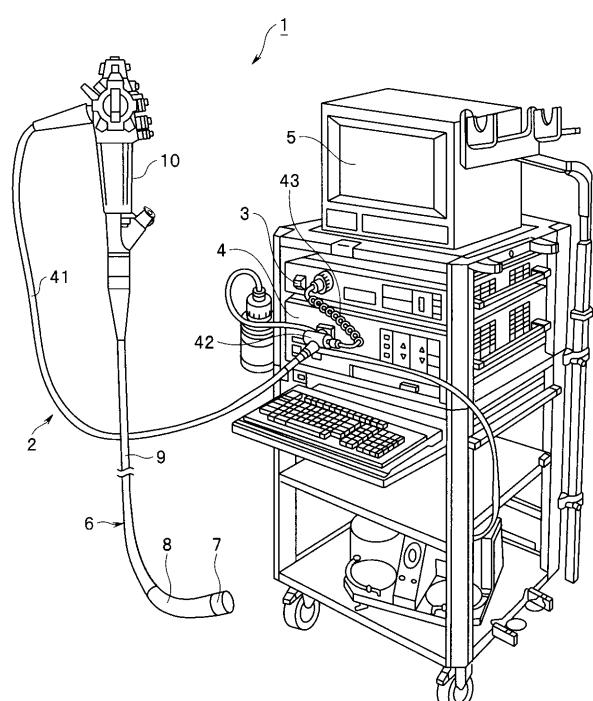

【図1】図1は、本発明の第1の実施形態の内視鏡を含む内視鏡システムの構成を示す図である。

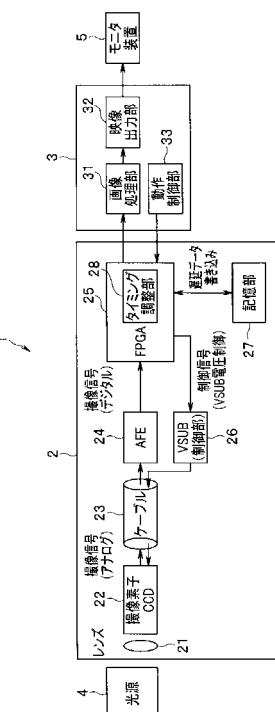

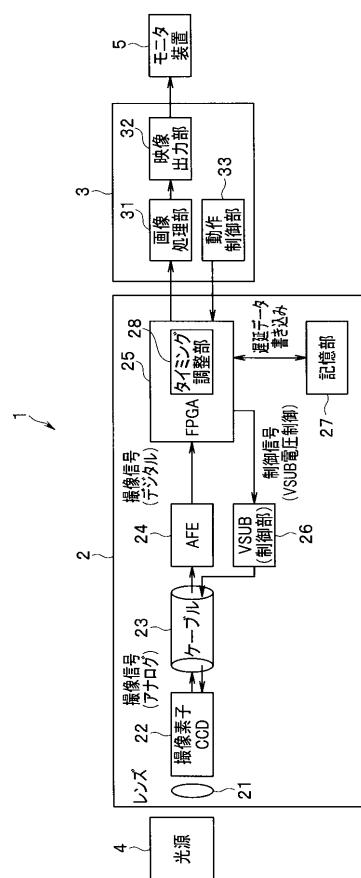

【図2】図2は、第1の実施形態の内視鏡を含む内視鏡システムの電気的な構成を示すブロック図である。

【図3】図3は、第1の実施形態の内視鏡における撮像素子およびの基板電圧VSB制御部の構成を示すブロック図である。

【図4】図4は、第1の実施形態の内視鏡において、内視鏡構造等に問題が無いとした場合における有効画素開始位置の算出工程を示すフローチャートである。 10

【図5】図5は、第1の実施形態の内視鏡において、内視鏡構造等に問題が無いとした場合における有効画素開始位置の算出工程を示すタイミングチャートである。

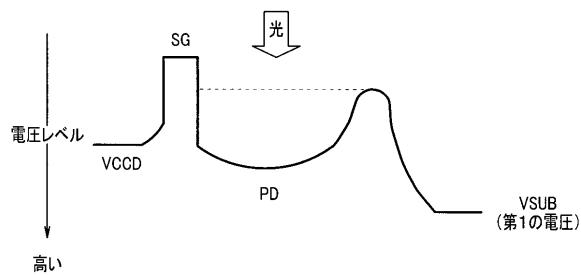

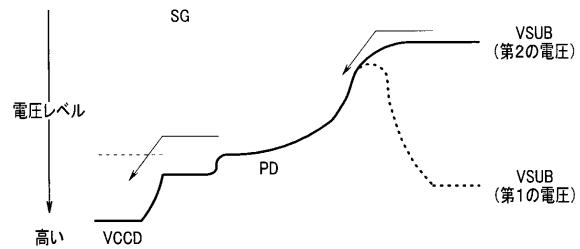

【図6】図6は、第1の実施形態の内視鏡において、内視鏡構造等に問題が無いとした場合における、露光時の固体撮像素子に係るポテンシャル図である。

【図7】図7は、第1の実施形態の内視鏡において、内視鏡構造等に問題が無いとした場合における、読み出し時の固体撮像素子に係るポテンシャル図である。

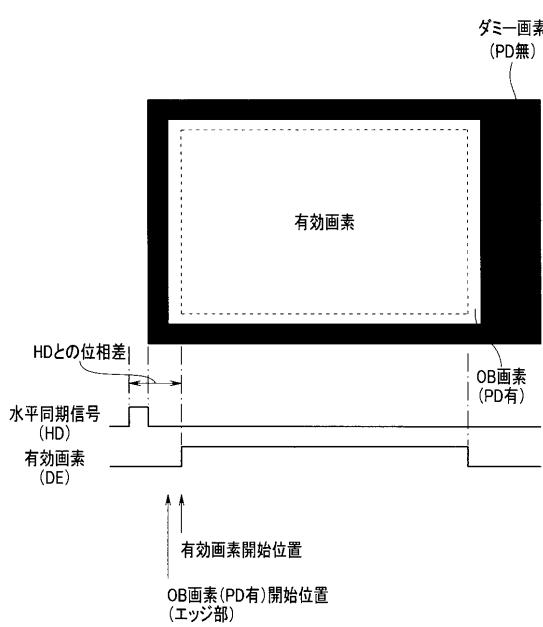

【図8】図8は、第1の実施形態の内視鏡において、水平同期信号と有効画素開始位置との位相差を求める際の様子を示したタイミングチャートである。 20

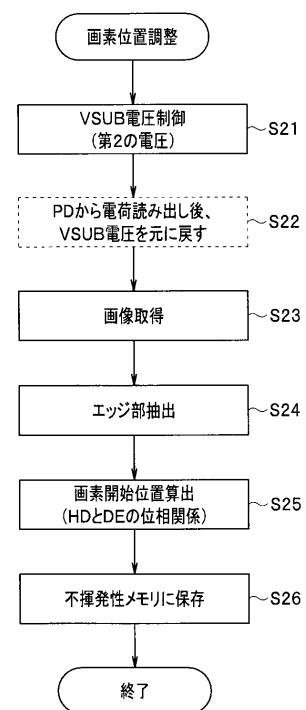

【図9】図9は、第1の実施形態の内視鏡における有効画素開始位置の算出工程を示すフローチャートである。

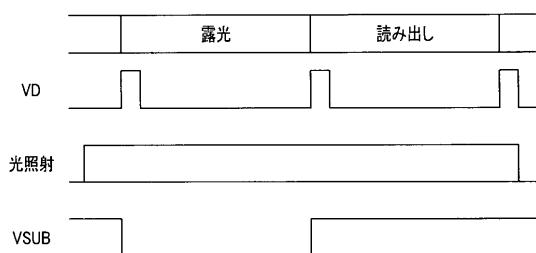

【図10】図10は、第1の実施形態の内視鏡における有効画素開始位置の算出工程を示すタイミングチャートである。

【図11】図11は、第1の実施形態の内視鏡の有効画素開始位置の算出工程における電荷の逆注入時の固体撮像素子に係るポテンシャル図である。 30

【図12】図12は、第1の実施形態の内視鏡の有効画素開始位置の算出工程における読み出し時の固体撮像素子に係るポテンシャル図である。

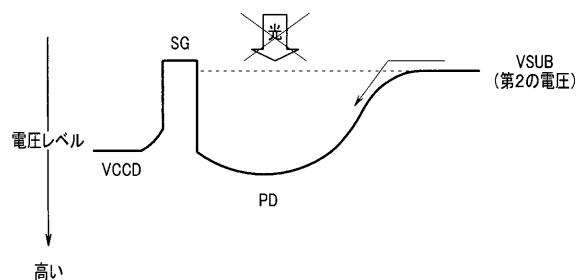

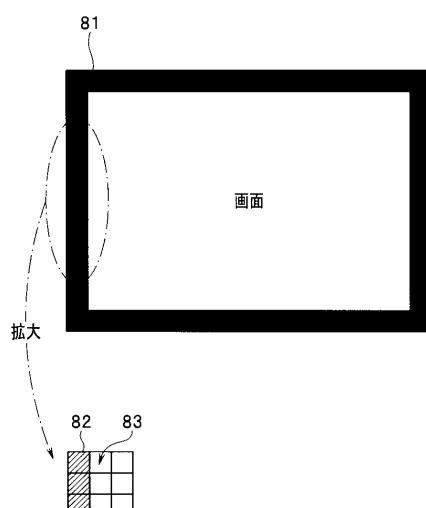

【図13】図13は、従来の内視鏡において、内視鏡自体の遮光構造、配光特性および組立精度に問題が無く、有効画素領域とOB画素領域との境界に光が適切に照射されている状態を示した説明図である。

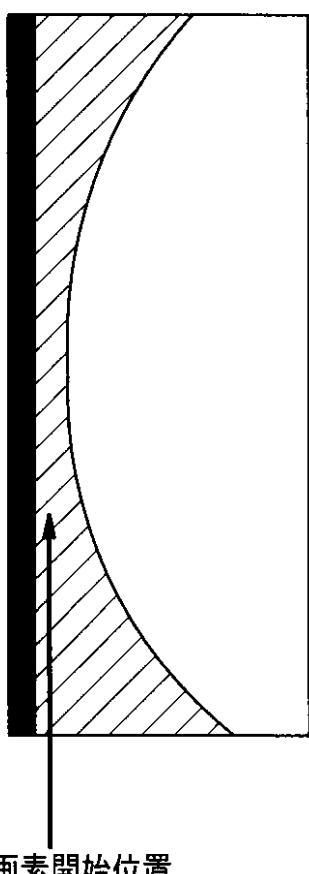

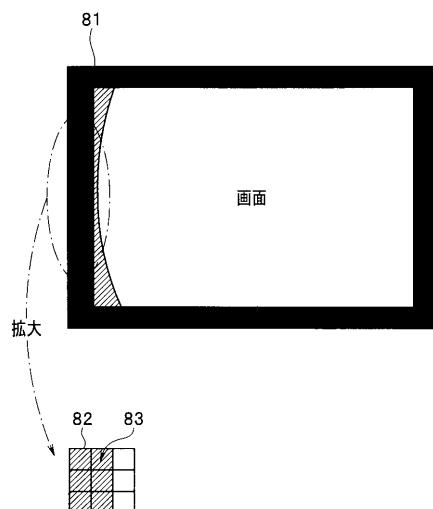

【図14】図14は、従来の内視鏡において、内視鏡自体の遮光構造、配光特性または組立精度に問題が有り、有効画素領域とOB画素領域との境界に光が十分に照射されていない状態を示した説明図である。

【図15】図15は、従来の内視鏡において、内視鏡自体の遮光構造、配光特性および組立精度に問題が無く、有効画素領域とOB画素領域との境界に光が適切に照射されている状態における有効画素開始位置を示した説明図である。

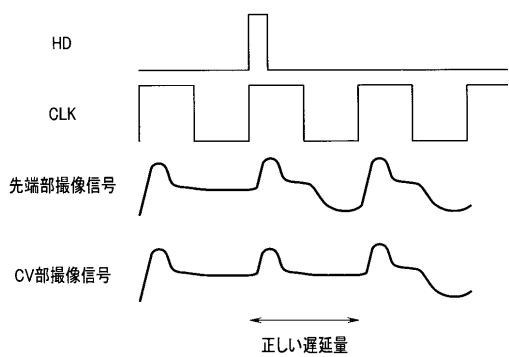

【図16】図16は、従来の内視鏡において、内視鏡自体の遮光構造、配光特性および組立精度に問題が無い状態における、伝送ケーブルによる撮像信号の遅延状態を示したタイミングチャートである。

【図17】図17は、従来の内視鏡において、内視鏡自体の遮光構造、配光特性または組立精度に問題が有り、有効画素領域とOB画素領域との境界に光が十分に照射されていない状態における有効画素開始位置を示した説明図である。 40

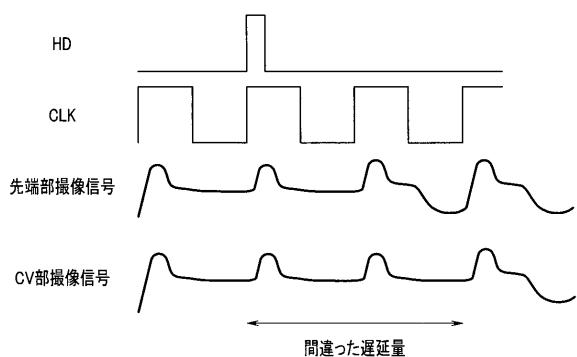

【図18】図18は、従来の内視鏡において、内視鏡自体の遮光構造、配光特性または組立精度に問題が有る状態における、伝送ケーブルによる撮像信号の遅延状態を示したタイミングチャートである。

**【発明を実施するための形態】**

**【0016】**

以下、図面を参照して本発明の実施形態を説明する。

**【0017】**

<第1の実施形態>

10

20

30

40

50

図1は、本発明の第1の実施形態の撮像装置を含む内視鏡システムの構成を示す図であり、図2は、第1の実施形態の撮像装置を含む内視鏡システムの電気的な構成を示すブロック図である。

#### 【0018】

なお、本実施形態においては、撮像装置として、固体撮像素子を有し被検体の内部の被写体を撮像する内視鏡を例に挙げて説明する。

#### 【0019】

図1、図2に示すように、本第1の実施形態の撮像装置（内視鏡）を有する内視鏡システム1は、被検体の観察し撮像する内視鏡2と、当該内視鏡2に接続され前記撮像信号を入力し所定の画像処理を施すビデオプロセッサ3と、被検体を照明するための照明光を供給する光源装置4と、撮像信号に応じた観察画像を表示するモニタ装置5と、を有している。10

#### 【0020】

内視鏡2は、被検体の体腔内等に挿入される細長の挿入部6と、挿入部6の基端側に配設され術者が把持して操作を行う内視鏡操作部10と、内視鏡操作部10の側部から延出するよう一方の端部が設けられたユニバーサルコード41と、を有して構成されている。20

#### 【0021】

挿入部6は、先端側に設けられた硬質の先端部7と、先端部7の後端に設けられた湾曲自在の湾曲部8と、湾曲部8の後端に設けられた長尺かつ可撓性を有する可撓管部9と、を有して構成されている。20

#### 【0022】

前記ユニバーサルコード41の基端側にはコネクタ42が設けられ、当該コネクタ42は光源装置4に接続されるようになっている。すなわち、コネクタ42の先端から突出する流体管路の接続端部となる口金（図示せず）と、照明光の供給端部となるライトガイド口金（図示せず）とは光源装置4に着脱自在で接続されるようになっている。30

#### 【0023】

さらに、前記コネクタ42の側面に設けた電気接点部には接続ケーブル43の一端が接続されるようになっている。そして、この接続ケーブル43には、例えば内視鏡2における撮像素子22（図2参照）からの撮像信号を伝送する信号線が内設され、また、他端のコネクタ部はビデオプロセッサ3に接続されるようになっている。30

#### 【0024】

なお、前記コネクタ42には、後述するAFE24、FPGA25、基板電圧VSUB制御部26および当該内視鏡2における固有の所定ID情報（例えば、遅延データ等）を記憶した記憶部27等（図2参照）が配設されている（これら各構成要素については、後に詳述する）。

#### 【0025】

ここで、本実施形態の内視鏡2の構成を説明するに先立って、本願発明の課題を明確にするために、内視鏡自体の遮光構造、配光特性または組立精度が、固体撮像素子における有効画素開始位置の算出に及ぼす影響について、図13～図18を参照して説明する。40

#### 【0026】

上述したように、伝送ケーブルに起因する、内視鏡固有の撮像信号に係る「正しい遅延量」を正確に求めるためには、固体撮像素子における有効画素開始位置を正確に算出することを要するが、内視鏡自体の遮光構造、配光特性または組立精度等により、この有効画素開始位置を正確に求めることが困難となる虞があった。

#### 【0027】

この場合、すなわち、有効画素開始位置を誤って認識してしまうと、上述した理由により、伝送ケーブルに起因する「遅延量」についても間違って認識しまうこととなり、上記の「正しい遅延量」を得ることができない虞があった。

#### 【0028】

図13、図15、図16は、従来の内視鏡において、内視鏡自体の遮光構造、配光特性および組立精度に問題が無く、有効画素領域とOB画素領域との境界に光が適切に照射されている状態を示した図であって、図15は、有効画素開始位置を示した説明図であり、図16は、伝送ケーブルによる撮像信号の遅延状態を示したタイミングチャートである。

【0029】

図13、図15に示すように、内視鏡自体の遮光構造、配光特性および組立精度に問題が無い状態において撮像素子に光を照射すると、有効画素領域（図15中、「画面」と表示）とOB画素領域81との境界には光が適切に照射されることとなる。

【0030】

すなわちこのとき、図15における有効画素領域とOB画素領域81との境界の拡大部が示すように、複数の画素のうちOB画素領域81における画素82に対して、直近の有効画素面の左端の画素83には適切に光が照射され、当該画素83からは適切に撮像信号が出力されることとなる。

10

【0031】

そしてこのとき内視鏡は、この画素83の位置を当該内視鏡における「有効画素開始位置」として算出することができる。

【0032】

ところで、上述したように、内視鏡先端部に配設された撮像素子からの撮像信号（図16においては、先端部撮像信号）は、伝送ケーブルにおいて所定の遅延を生じることとなり、例えば、図16に示す水平同期信号に対して、後段側（図16においてはCV部（ビデオプロセッサ3）撮像信号）において1クロック分の遅延を生じることとなる。

20

【0033】

ここで、上述したように、有効画素開始位置を正確に算出できている以上、この遅延分（今の場合1クロック分）は、内視鏡固有の情報として正しく認識できるため、後段側において支障を来すことはない。

【0034】

一方、内視鏡自体の遮光構造、配光特性または組立精度に問題が有り、有効画素領域とOB画素領域との境界に光が十分に照射されていない状態を考える。

【0035】

図14、図17、図18は、従来の内視鏡において、内視鏡自体の遮光構造、配光特性または組立精度に問題が有り、有効画素領域とOB画素領域との境界に光が十分に照射されていない状態を示した図であって、図17は、有効画素開始位置を示した説明図であり、図18は、伝送ケーブルによる撮像信号の遅延状態を示したタイミングチャートである。

30

【0036】

図14、図17に示すように、内視鏡自体の遮光構造、配光特性および組立精度に問題が有る状態において撮像素子に光を照射すると、有効画素領域（図17中、「画面」と表示）とOB画素領域81との境界には光が十分に照射されないこととなる（図17中、斜線部分）。

40

【0037】

すなわちこのとき、図17における有効画素領域とOB画素領域81との境界の拡大部が示すように、複数の画素のうちOB画素領域81における画素82に対して、直近の有効画素面の左端の画素83には十分に光が照射されておらず、当該画素83からは撮像信号が出力されない虞がある。

【0038】

このとき内視鏡は、この画素83を有効画素開始位置として算出することはなく、さらに右方向の画素（例えば、右隣の画素）の位置を当該内視鏡における「有効画素開始位置」として算出することとなる。

【0039】

そして、もともと伝送ケーブルの遅延量が1クロック分である内視鏡の場合において、

50

上述したように正しく有効画素開始位置を算出することができずに例えば、画素 8 3 の右隣の画素の位置を有効画素開始位置と算出してしまった遅延量（例えば、2 クロック分の遅延量；図 18 参照）として認識される虞がある。

#### 【0040】

そして、この「正しい遅延量」を得ることができない場合、後段の画像処理において、例えば、色ずれ、または、レンズとの中心位置ずれという不具合を生じる虞がある。

#### 【0041】

本願発明は、上述した事情に鑑みてなされたものであり、内視鏡自体の遮光構造、配光特性または組立精度等によらず、固体撮像素子における有効画素開始位置を正確に算出することができる撮像装置（内視鏡）を提供するものである。

10

#### 【0042】

図 2 に戻って、内視鏡 2 は、挿入部 6 の先端部 7 に配設された、被写体像を入光するレンズを含む対物光学系 21 と、対物光学系 21 における結像面に配設された撮像素子 22 と、を備える。

#### 【0043】

また内視鏡 2 は、撮像素子 22 から延出され、当該撮像素子 22 から挿入部 6 、操作部 10 、ユニバーサルコード 41 を経て、コネクタ 42 に至るまで配設されたケーブル 23 を備える。

#### 【0044】

さらに内視鏡 2 は、ケーブル 23 の後端側であってコネクタ 42 に配設された、A F E 24 、F P G A 25 、基板電圧 V S U B 制御部 26 、記憶部 27 等を有する。

20

#### 【0045】

撮像素子 22 は、本実施形態においては C C D イメージセンサにより構成される。また、入射光に応じて光を光電変換して信号電荷を生成する複数の光電変換部であるフォトダイオード（P D）を有し、当該光電変換部において生成した信号電荷に基づいて撮像信号を生成し出力するための複数の画素を備える。

#### 【0046】

そして撮像素子 22 は、被写体からの光学像が撮像面に結像されると、各画素に入射した光を光電変換部において光電変換してアナログ撮像信号を出力するようになっている。

30

#### 【0047】

また、撮像素子 22 は、基板電圧（V S U B）を出力する出力端（V S U B 出力端）を備えており、当該 V S U B 出力端は、ケーブル 23 を経由して基板電圧 V S U B 制御部 26 に接続されるようになっている（基板電圧 V S U B 制御部 26 については、後に詳述する）。

#### 【0048】

ケーブル 23 は、撮像素子 22 の駆動信号および当該撮像素子 22 からのアナログの撮像信号を伝送するケーブルであり、本実施形態においては、撮像素子 22 からコネクタ 42 に至るまで配設されている。

#### 【0049】

また、ケーブル 23 を伝送するアナログ撮像信号は、上述したように、当該ケーブル 23 において所定の遅延を生じることとなる（図 16 等参照）。

40

#### 【0050】

A F E（アナログフロントエンド）24 は、ケーブル 23 を経たアナログ撮像信号に対して所定の処理を行う回路であり、公知の C D S（Correlation Double Sampling）回路およびアナログ / デジタル変換器（A D）等を備え、当該撮像信号をデジタル撮像信号として出力する。

#### 【0051】

F P G A 25 は、いわゆる Field Programmable Gate Array により構成され、ビデオプロセッサ 3 からの動作制御を受け、各種のタイミング調整を行うタイミング調整部 28 を形成する。

50

## 【0052】

また、後述するようにFPGA25は、基板電圧V<sub>SUB</sub>制御部26に対してV<sub>SUB</sub>制御信号を送出する役目を果たすようになっている。

## 【0053】

基板電圧V<sub>SUB</sub>制御部26は、撮像素子22に接続され、本願発明の特徴をなす基板電圧V<sub>SUB</sub>を制御する。

## 【0054】

<基板電圧制御部および有効画素開始位置算出部について>

以下、基板電圧制御部である基板電圧V<sub>SUB</sub>制御部26および有効画素開始位置算出部であるFPGA25について詳しく説明する。

10

## 【0055】

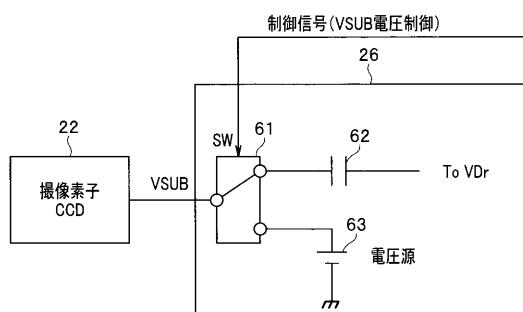

図3は、第1の実施形態の内視鏡における撮像素子22およびの基板電圧V<sub>SUB</sub>制御部26の構成を示すブロック図である。

## 【0056】

図3に示すように基板電圧V<sub>SUB</sub>制御部26は、撮像素子22における前記V<sub>SUB</sub>出力端に接続されると共に、FPGA25からの制御信号が入力される基板電圧V<sub>SUB</sub>切替部61と、基板電圧V<sub>SUB</sub>切替部61の一出力端に接続されると共に、垂直同期信号ドライバに接続される出力コンデンサ62と、基板電圧V<sub>SUB</sub>切替部61の他の出力端に接続されたV<sub>SUB</sub>切替用電圧源63と、を備える。

20

## 【0057】

基板電圧V<sub>SUB</sub>切替部61は、FPGA25からの制御信号（V<sub>SUB</sub>電圧制御）により切り替えられるスイッチであり、撮像素子22の基板電圧V<sub>SUB</sub>を、内視鏡2内部電圧である第1の電圧と（図3におけるスイッチ状態）、当該第1の電圧とは異なる第2の電圧とのいずれかに設定することができるようになっている。

## 【0058】

V<sub>SUB</sub>切替用電圧源63は、前記基板電圧V<sub>SUB</sub>切替部61のスイッチが当該電圧源側に切り替わった際に、撮像素子22の基板電圧V<sub>SUB</sub>が前記第2の電圧に設定可能となるような電圧源である。

30

## 【0059】

具体的に前記第2の電圧は、前記第1の電圧より低い電圧であって撮像素子22における光電変換部（フォトダイオードPD）に電荷を逆注入可能とする電圧である。

## 【0060】

また、FPGA25は、上述したように、基板電圧V<sub>SUB</sub>制御部26に対してV<sub>SUB</sub>制御信号を送出する役目を果たすと共に、撮像素子22から出力した前記撮像信号のエッジを抽出し、前記複数の画素に係る有効画素開始位置を算出する有効画素開始位置算出部としての役目を果たす。

40

## 【0061】

さらにFPGA25は、撮像素子22が遮光された状態（例えば、工場出荷時等）において、前記基板電圧V<sub>SUB</sub>を前記第2の電圧に設定するよう前記基板電圧V<sub>SUB</sub>切替部61を制御して前記光電変換部PDに電荷が逆注入された状態にせしめた後、撮像素子22から出力した前記撮像信号のエッジを抽出し、前記複数の画素に係る有効画素開始位置を算出することを可能とする。

40

## 【0062】

なお、本実施形態においては、工場出荷時等において撮像素子22が遮光された状態で前記光電変換部PDに電荷を逆注入し、撮像素子22から出力した撮像信号のエッジを抽出し、前記複数の画素に係る有効画素開始位置を算出するものとした。

## 【0063】

しかしながら、本願発明は、撮像素子22が遮光されているかいないか関わらず、前記光電変換部PDに電荷を逆注入することで、撮像信号のエッジを抽出し、有効画素開始位置を算出することができる。

50

## 【0064】

記憶部27は、当該内視鏡2における固有の情報、例えば、例えば、ケーブル23に起因する遅延データ等を不揮発的に記憶する記憶部である。

## 【0065】

<有効画素開始位置の算出方法>

次に、本実施形態における有効画素開始位置の算出方法について説明する。

## 【0066】

まず、内視鏡自体の遮光構造、配光特性および組立精度等に問題が無いとした場合における有効画素開始位置の算出工程について説明する。

## 【0067】

10

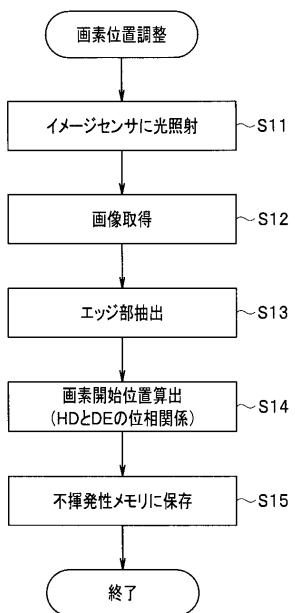

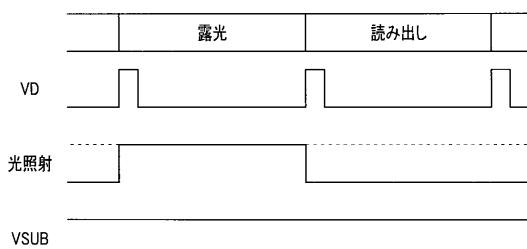

図4は、第1の実施形態の内視鏡において、内視鏡構造等に問題が無いとした場合の、有効画素開始位置の算出工程を示すフローチャートであり、図5は、同タイミングチャートである。

## 【0068】

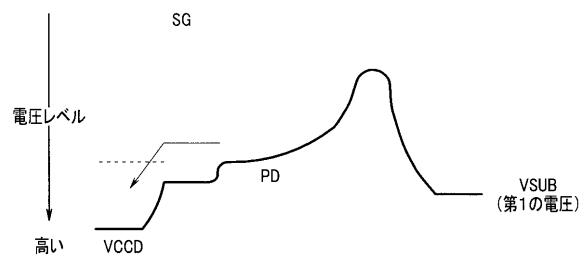

また、図6は、同じく内視鏡構造等に問題が無いとした場合における、露光時の固体撮像素子に係るポテンシャル図であり、図7は、読み出し時の固体撮像素子に係るポテンシャル図である。

## 【0069】

20

さらに、図8は、第1の実施形態の内視鏡において、水平同期信号(HD)と有効画素(DE)における有効画素開始位置との位相差を求める際の様子を示したタイミングチャートである。

## 【0070】

図4、図5に示すように、工場出荷維時において撮像素子22に所定の光が照射されると(ステップS11)、撮像素子22は露光制御と共に読み出し制御され、所定の画像情報を取得する(ステップS12)。

## 【0071】

30

このとき、FPGA25からの制御信号により基板電圧VSUB切替部61は前記第1の電圧側(図3に示す状態)に設定され、すなわち、撮像素子22の基板電圧VSUBは、当該内視鏡2の内部電圧である第1の電圧に設定された状態にある。

## 【0072】

また、撮像素子22における露光時においては、図6のポテンシャル図に示すように、光電変換部であるフォトダイオードPDのポテンシャル井戸には、照射された光量に応じて電荷が発生することとなる。

## 【0073】

続いて撮像素子22における読み出し時においては、内視鏡2は、読み出しゲートを制御し、図7のポテンシャル図に示すように、フォトダイオードPDと垂直転送路VCCDとの間のポテンシャル障壁を低くし、フォトダイオードPDに貯められた電荷を垂直転送路VCCDに向けて移動する。

## 【0074】

40

その後、内視鏡2におけるFPGA25は、撮像素子22において取得した画像からエッジ部(OB画素(PD有り)の開始位置)を抽出し(ステップS13)、抽出したエッジ部の画素位置から有効画素開始位置を算出すると共に、当該有効画素開始位置と水平同期信号との位相差を求める(図4のステップS14および図8参照)。

## 【0075】

ここで、OB画素(PD有り)の開始位置から有効画素までの距離は、内視鏡ごと(撮像素子ごと)に決まる値であるため、抽出したエッジ部位置(OB画素の開始位置)から有効画素開始位置を算出することが可能となる。

## 【0076】

50

なお、本実施形態においては、OB画素としてPD有りのものと採用したが、仮にOB画素としてPDが無い場合は、抽出したエッジ部が有効画素開始位置となる。

**【 0 0 7 7 】**

この後、内視鏡2は、算出した有効画素開始位置および前記位相差の情報から、当該内視鏡2に係る「遅延量」のデータを求め、当該遅延量のデータを記憶部27に記憶する(ステップS15)。

**【 0 0 7 8 】**

次に、内視鏡自体の遮光構造、配光特性および組立精度等に問題が有る場合であっても対応可能な本実施形態における有効画素開始位置の算出工程について説明する。

**【 0 0 7 9 】**

図9は、第1の実施形態の内視鏡における有効画素開始位置の算出工程を示すフロー10チャートであり、図10は、同タイミングチャートである。

**【 0 0 8 0 】**

また、図11は、第1の実施形態の内視鏡の有効画素開始位置の算出工程における電荷の逆注入時の固体撮像素子に係るポテンシャル図であり、図12は、同読み出し時の固体撮像素子に係るポテンシャル図である。さらに、図8は、第1の実施形態の内視鏡において、水平同期信号(HD)と有効画素(DE)における有効画素開始位置との位相差を求める際の様子を示したタイミングチャートである。

**【 0 0 8 1 】**

図9、図10に示すように、本実施形態の内視鏡2は、工場出荷維時における撮像素子22が遮光状態の際に、FPGA25からの制御信号により基板電圧V<sub>SUB</sub>切替部61をV<sub>SUB</sub>切替用電圧源63側に設定する。このとき、撮像素子22の基板電圧V<sub>SUB</sub>は、V<sub>SUB</sub>切替用電圧源63に応じた第2の電圧(第1の電圧より低い電圧)に設定される(ステップS21)。

**【 0 0 8 2 】**

ここで、撮像素子22の基板電圧V<sub>SUB</sub>が第2の電圧に設定された際、撮像素子22は遮光状態にあって光が照射されるものではないのだが、図11のポテンシャル図に示すように、光電変換部であるフォトダイオードPDのポテンシャル井戸には、当該第2の電圧に応じた電荷が逆注入され、あたかも光が照射された如く電荷が貯まることとなる。

**【 0 0 8 3 】**

この後、内視鏡2は、撮像素子22における読み出し時においては、読み出しゲートを制御し、図12のポテンシャル図に示すように、フォトダイオードPDと垂直転送路VCDとの間のポテンシャル障壁を低くし、フォトダイオードPDに貯められた電荷を垂直転送路VCCDに向けて移動する。

**【 0 0 8 4 】**

上述した工程によりフォトダイオードPDから電荷を読み出した後、FPGA25の制御により基板電圧V<sub>SUB</sub>切替部61を前記第1の電圧側(図3に示す状態)に設定し、すなわち、撮像素子22の基板電圧V<sub>SUB</sub>を、当該内視鏡2の内部電圧である第1の電圧に戻し(ステップS22)、撮像素子22から上記同様に画像を取得する。

**【 0 0 8 5 】**

その後、内視鏡2におけるFPGA25は、上記同様に、撮像素子22において取得した画像からエッジ部(OB画素(PD有り)の開始位置)を抽出し(ステップS24)、抽出したエッジ部の画素位置から有効画素開始位置を算出すると共に、当該有効画素開始位置と水平同期信号との位相差を求める(図9のステップS25および図8参照)。

**【 0 0 8 6 】**

この後、内視鏡2は、算出した有効画素開始位置および前記位相差の情報から、上記同様に当該内視鏡2に係る「遅延量」のデータを求め、当該遅延量のデータを記憶部27に記憶する(ステップS26)。

**【 0 0 8 7 】**

以上説明したように、本実施形態においては、撮像素子22の有効画素開始位置を算出する工程において、撮像素子22の基板電圧V<sub>SUB</sub>を切り替えることにより光電変換部であるフォトダイオードPDに対して電荷を逆注入する工程を設けることで、撮像素子2

2に照射される光によらず、有効画素開始位置を正確に算出することができる。

【0088】

換言すれば、内視鏡自体の遮光構造、配光特性または組立精度に問題が有り、有効画素領域とO B画素領域との境界に光が十分に照射されていない状態が発生し得る場合であっても、有効画素開始位置を正確に算出することを可能とし、ひいては、ケーブルに起因する撮像信号の遅延量を「正しい遅延量」として求めることができる。

【0089】

本発明は、上述した実施形態に限定されるものではなく、本発明の要旨を変えない範囲において、種々の変更、改変等が可能である。

【符号の説明】

【0090】

1 ... 内視鏡システム

2 ... 内視鏡

3 ... ビデオプロセッサ

4 ... 光源

5 ... モニタ装置

2 1 ... 対物光学系

2 2 ... 撮像素子

2 3 ... ケーブル

2 4 ... アナログフロントエンド回路 (AFE)

2 5 ... FPGAs

2 6 ... 基板電圧VSB制御部

2 7 ... 記憶部

2 8 ... タイミング調整部

3 1 ... 画像処理部

3 2 ... 映像出力部

3 3 ... 動作制御部

6 1 ... 基板電圧VSB切替部

6 3 ... VSB切替用電圧源

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図 1 0】

【図 1 2】

【図 1 1】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 7】

【図 1 8】

---

フロントページの続き

|                                |               |            |

|--------------------------------|---------------|------------|

| (51) Int.CI.                   | F I           | テーマコード(参考) |

| <b>G 0 2 B 23/24 (2006.01)</b> | G 0 2 B 23/24 | B          |

F ターム(参考) 5C024 AX02 BX02 CY25 CY44 CY46 GY01 HX47 JX41

5C122 EA57 FB23 FH03 GE06 GE10 GE23 GE25 HB02

|                |                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 摄像装置                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2017120972A</a>                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2017-07-06 |

| 申请号            | JP2015256222                                                                                                                                                                                                                                                                                             | 申请日     | 2015-12-28 |

| [标]申请(专利权)人(译) | 奥林巴斯株式会社                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 奥林巴斯公司                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 本田誠也                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 本田 誠也                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | H04N5/341 H04N5/351 H04N5/372 H04N5/232 A61B1/04 G02B23/24                                                                                                                                                                                                                                               |         |            |

| FI分类号          | H04N5/335.410 H04N5/335.510 H04N5/335.720 H04N5/232.Z A61B1/04.372 G02B23/24.B A61B1/045.610 A61B1/05 H04N5/225.300 H04N5/225.500 H04N5/232 H04N5/341 H04N5/351 H04N5/372                                                                                                                                |         |            |

| F-TERM分类号      | 2H040/GA00 4C161/BB02 4C161/CC06 4C161/DD03 4C161/JJ11 4C161/LL02 4C161/NN01 4C161/NN03 4C161/SS03 4C161/UU03 4C161/UU09 5C024/AX02 5C024/BX02 5C024/CY25 5C024/CY44 5C024/CY46 5C024/GY01 5C024/HX47 5C024/JX41 5C122/EA57 5C122/FB23 5C122/FH03 5C122/GE06 5C122/GE10 5C122/GE23 5C122/GE25 5C122/HB02 |         |            |

| 代理人(译)         | 伊藤 进<br>长谷川 靖<br>ShinoUra修                                                                                                                                                                                                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                |         |            |

## 摘要(译)

要解决的问题：无论光屏蔽结构，光分布特性或内窥镜本身的组装精度如何，精确计算固态成像装置中的有效像素起始位置。一种成像装置，包括：成像装置，包括：多个像素，用于基于在光电转换单元中产生的信号电荷产生和输出成像信号；以及控制单元，用于基于第一电压和第一电压控制成像装置22的基板电压VSUB，并且第二电压低于像素电压VSUB的电压并且能够将电荷反向注入光电转换单元，以及基板电压VSUB控制单元26，其产生图像信号的边缘并且，计算有效像素开始位置的FPGA25通过将基板电压VSUB设定为第二电压并使光电转换单元处于反向注入电荷的状态来计算有效像素开始位置之后，提取边缘并计算有效像素开始位置。.The